# **GI-Edition**

Lecture Notes in Informatics

Gero Mühl, Jan Richling, Andreas Herkersdorf (Hrsg.)

## **ARCS 2012 Workshops**

28. Februar – 2. März 2012 München

Proceedings

200

## Gero Mühl, Jan Richling, Andreas Herkersdorf (Hrsg.)

## **ARCS 2012 Workshops**

28. Februar – 2. März 2012 München, Germany

Gesellschaft für Informatik e.V. (GI)

#### Lecture Notes in Informatics (LNI) - Proceedings

Series of the Gesellschaft für Informatik (GI)

Volume P-200

ISBN 978-3-88579-294-9 ISSN 1617-5468

#### **Volume Editors**

Prof. Dr.-Ing. Gero Mühl Universität Rostock Albert-Einstein-Straße 22 18051 Rostock, Germany Email: gero.muehl@uni-rostock.de

Dr.-Ing. Jan Richling Technische Universität Berlin Einsteinufer 17 10587 Berlin, Germany Email: <u>richling@cs.tu-berlin.de</u>

Prof. Dr. sc.techn. Andreas Herkersdorf Technische Universität München Arcisstraße 21 80290 München, Germany

#### Series Editorial Board

Heinrich C. Mayr, Alpen-Adria-Universität Klagenfurt, Austria (Chairman, mayr@ifit.uni-klu.ac.at) Hinrich Bonin, Leuphana Universität Lüneburg, Germany Dieter Fellner, Technische Universität Darmstadt, Germany Ulrich Flegel, Hochschule Offenburg, Germany Ulrich Frank, Universität Duisburg-Essen, Germany Johann-Christoph Freytag, Humboldt-Universität zu Berlin, Germany Michael Goedicke, Universität Duisburg-Essen, Germany Ralf Hofestädt, Universität Bielefeld, Germany Michael Koch, Universität der Bundeswehr München, Germany Axel Lehmann, Universität der Bundeswehr München, Germany Ernst W. Mayr, Technische Universität München, Germany Sigrid Schubert, Universität Siegen, Germany Martin Warnke, Leuphana Universität Lüneburg, Germany

#### Dissertations

Steffen Hölldobler, Technische Universität Dresden, Germany Seminars Reinhard Wilhelm, Universität des Saarlandes, Germany

## Thematics

Andreas Oberweis, Karlsruher Institut für Technologie (KIT), Germany

© Gesellschaft für Informatik, Bonn 2012 **printed by** Köllen Druck+Verlag GmbH, Bonn

## Message from the Chairs

The conference on Architecture of Computing Systems (ARCS) has a long and prestigious history in computing systems. Five workshops are co-located with the conference covering a large field of topics. The papers of the following workshops are included in these proceedings:

#### ASPRIT

Workshop on Architectures for Self-Organizing Private IT-Spheres

CSECS

Workshop on Complex Sciences in the Engineering of Computing Systems PARMA

3rd Workshop on Parallel Programming and Run-Time Management Techniques for Many-core Architectures

PASA

10th Workshop on Parallel Systems and Algorithms

VERFE

8th Workshop on Dependability and Fault-Tolerance

For each of these workshops, the workshop committees selected high quality contributions within a competitive peer review process. Many thanks go to the organizers of the workshops: Detlef Krömker, Ralf Dörner, Uwe Brinkschulte, Ingo Scholtes, Claudio J. Tessone, Jacob Beal, Alex Bartzas, Giovanni Agosta, Jörg Keller, Rolf Wanka, Karl-Erwin Großpietsch, and Jörg Henkel.

In addition to the workshops, the conference also features tutorials on "Organic Computing: Status and Outlook" as well as on "Partial Reconfiguration of FPGAs in Practice -Tools and Applications". A paper related to the latter tutorial is included in this proceedings. We are grateful to the people that made these tutorials possible: Christian Beckhoff, Volker Breuer, Christopher Dennl, Michael Feilen, Dirk Koch, Christian Mueller-Schloer, Hartmut Schmeck, Walter Stechele, Juergen Teich, Jim Torresen, and Daniel Ziener.

The workshop and tutorial program would not have been possible without the help of many people: The program co-chairs Uwe Brinkschulte and Kay Roemer, the local and publication chair Walter Stechele and the financial chair Thomas Wild. We would also like to thank Cornelia Winter (GI) and Jürgen Kuck (Köllen Verlag) for the uncomplicated and flexible handling of the proceedings publication process. Our final thank goes to all the authors for their contributions that make this an attractive workshop program. We wish you all interesting discussions during the two days of workshops and tutorials.

| Gero Mühl           | ARCS 2012 Workshop Chair |

|---------------------|--------------------------|

| Jan Richling        | ARCS 2012 Tutorial Chair |

| Andreas Herkersdorf | ARCS 2012 General Chair  |

## **Table of Contents**

| <b>XX71 1</b> | · · · · · · · · · · · · · · · · · · · | C C . 1C  | 0          | D.:     | TT Culture |

|---------------|---------------------------------------|-----------|------------|---------|------------|

| worksnop      | on Architectures                      | for Self- | Organizing | Private | 11-Spheres |

| Jan Schäfer, Reinhold Kröger, Simone Meixler, Uwe Brinkschulte<br>QoS-based Testing and Selection of Semantic Services                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Yuta Miyauchi, Noriko Matsumoto, Norihiko Yoshida, Yuko Kamiya,<br>Toshihiko Shimokawa<br>Adaptive Content Distribution Network for Live and On-Demand Streaming                                                           |

| <b>George Moldovan, Anda Ignat</b><br>An Anonymous Efficient Private Set Intersection Protocol for Wireless Sensor<br>Networks                                                                                             |

| <b>Tatsuya Abe, Yutaka Arakawa, Shigeaki Tagashira, Akira Fukuda</b><br>A Mobile Sink-initiated Proactive Routing Protocol for Deadline-Aware Data<br>Aggregation Method in Energy-Efficient Wireless Sensor Networks      |

| <b>Richard M. Zahoransky, Klaus Rechert, Konrad Meier, Dennis Wehrle,</b><br><b>Dirk Von Suchodoletz</b><br><i>Cellular Location Determination - Reliability and Trustworthiness of GSM</i><br><i>Location Data</i>        |

| Matthias Pfeiffer, Claudia Stockhausen, Katharina Reitz,<br>Detlef Krömker<br>Physiological Data in Future Livinig Environments                                                                                            |

| Sebastian Schmitt, Johannes Luderschmidt, Nadia Haubner,<br>Simon Lehmann, Ralf Dörner, Ulrich Schwanecke<br>Goal-Snapping: An Empirical Evaluation of Object Snapping in Tangible and<br>Multi-Touch Interfaces           |

| <b>Tomohiro Iwamoto, Shigeaki Tagashira, Yutaka Arakawa,<br/>Akira Fukuda</b><br>A Robust Generation Technique of Common Information Based on<br>Characteristic of Multipath Fading Channel by Shaking Handheld<br>Devices |

| Simon Lehmann, Jan Schäfer, Ralf Dörner, Ulrich Schwanecke<br>Towards Integration of User Interaction and Context Event Processing in<br>Intelligent Living Environments                                                   |

| Daniel Schiffner, Detlef Krömker Perception-influenced Animation                                                                                                                                                           |

| Nadia Haubner, Ulrich Schwanecke, Ralf Dörner, Simon Lehmann,<br>Johannes Luderschmidt<br>Towards a Top-View Detection of Body Parts in an Interactive Tabletop<br>Environment                                             |

| 1 <sup>st</sup> International Workshop on Complex Sciences in the Engineering of Computing Systems                                                                                 |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Aimee Gotway Bailey, Quan Minh Bui, J. Doyne Farmer,<br>Robert M. Margolis, Ramamoorthy Ramesh<br>Forecasting Technological Innovation                                             | 1 |

| Shota Ishikawa, Yutaka Arakawa, Shigeaki Tagashira, Akira Fukuda<br>Hot Topic Detection in Local Areas Using Twitter and Wikipedia                                                 | 1 |

| Marcelo Serrano Zanetti, Frank Schweitzer<br>A Network Perspective on Software Modularity                                                                                          | 1 |

| Workshop on Dependability and Fault Tolerance                                                                                                                                      |   |

| Bernhard Fechner, Arne Garbade, Sebastian Weis, Theo Ungerer<br>Fault Localization in NoCs by Timed Heartbeats                                                                     | 1 |

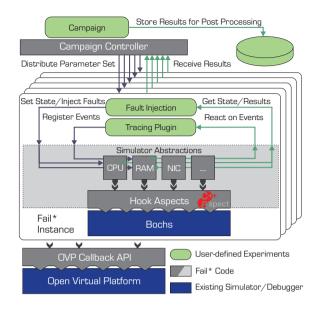

| Horst Schirmeier, Martin Hoffmann, Rüdiger Kapitza, Daniel Lohmann,<br>Olaf Spinczyk<br>Fail*: Towards a Versatile Fault Injection Experiment Framework                            | 2 |

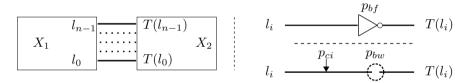

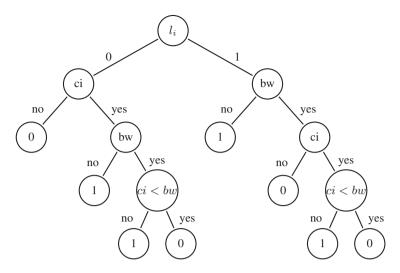

| <b>David Neuhäuser, Eberhard Zehendner</b><br>Correction of Faulty Signal Transmission for Resilient Designs of<br>Signed-Digit Arithmetic                                         | 2 |

| <b>Raphael Maas, Erik Maehle</b><br>Fault Tolerant and Adaptive Path Planning in Crowded Environments for<br>Mobile Robots Based on Hazard Estimation via Health Signals           | 2 |

| Karl-Erwin Großpietsch, Tanya A. Silayeva<br>ART Networks as Flexible Means to Implement Dependability Properties in<br>Autonomous Systems                                         | 2 |

| Raimar Lill, Francesca Saglietti<br>Model-based Testing of Autonomous Systems based on Coloured Petri Nets                                                                         | 2 |

| <b>Sebastian Müller, Mario Schölzel, Heinrich Theodor Vierhaus</b><br>Hierarchical Self-repair in Heterogeneous Multi-core Systems by Means of a<br>Software-based Reconfiguration | 2 |

| Holm Rauchfuss, Thomas Wild, Andreas Herkersdorf<br>Enhanced Reliability in Tiled Manycore Architectures through Transparent<br>Task Relocation                                    | 2 |

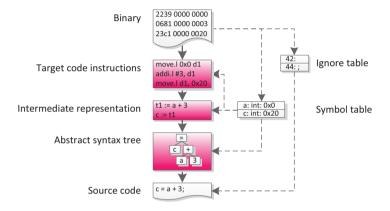

| <b>Dennis Obermann, Josef Börcsök</b><br>Two-Way-Compiler: Additional Data Saving for Generating the Original<br>Source Code of a Binary Program                                   | 2 |

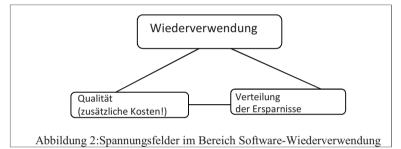

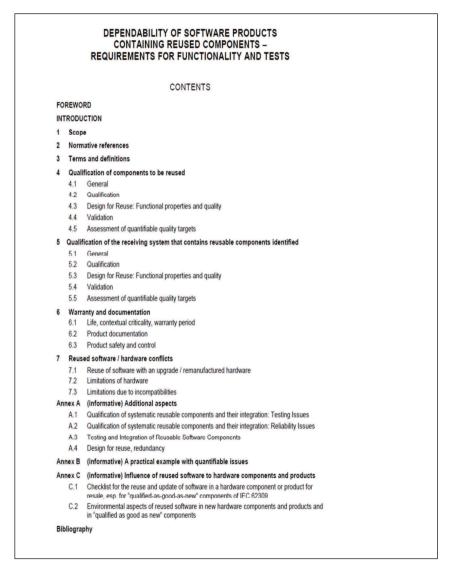

| <b>Fevzi Belli</b><br>Verlässlichkeit bei Wiederverwendung von IT-Komponenten – zum Stand der<br>Normungsaktivitäten                                                               | 2 |

## Tutorial on Reconfigurable Systems

| Dirk Koch, Jim Torresen, Christian Beckhoff, Daniel Ziener,<br>Christopher Dennl, Volker Breuer, Jürgen Teich, Michael Feilen,<br>Walter Stechele                                                                        |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Partial Reconfiguration on FPGAs in Practice - Tools and Applications                                                                                                                                                    | 297 |

| 3rd Workshop on Parallel Programming and Run-Time Management<br>Techniques for Many-core Architectures                                                                                                                   |     |

| Ioannis Koutras, Alexandros Bartzas, Dimitrios Soudris<br>Efficient Memory Allocations on a Many-Core Accelerator                                                                                                        | 327 |

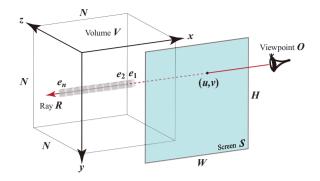

| Yuki Sugimoto, Fumihiko Ino, Kenichi Hagihara<br>Improving Cache Locality for Ray Casting with CUDA                                                                                                                      | 339 |

| Lazaros Papadopoulos, Alexandros Bartzas, Dimitrios Soudris<br>Run-Time Dynamic Data Type Transformations                                                                                                                | 351 |

| <b>Giovanni Mariani, Gianluca Palermo, Vittorio Zaccaria, Cristina Silvano</b><br><i>Evaluating Run-time Resource Management Policies for Multi-core</i><br><i>Embedded Platforms with the EMME Evaluation Framework</i> | 363 |

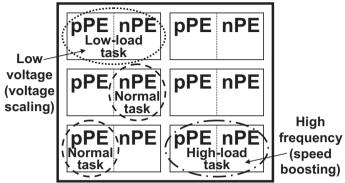

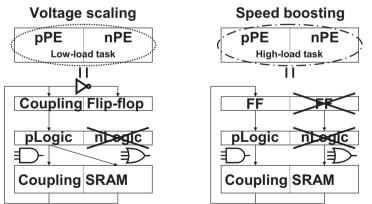

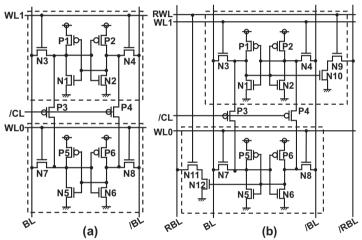

| Koji Kugata, Shinpei Soda, Yohei Nakata, Shunsuke Okumura,<br>Shintaro Izumi, Masahiko Yoshimoto, Hiroshi Kawaguchi<br>Processor Coupling Architecture for Aggressive Voltage Scaling on<br>Multicores                   | 375 |

| <b>Giovanni Agosta, Alessandro Barenghi, Gerardo Pelosi</b><br>Exploiting Bit-level Parallelism in GPGPUs: a Case Study on KeeLoq<br>Exhaustive Search Attacks                                                           | 385 |

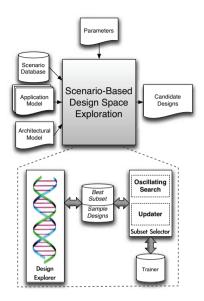

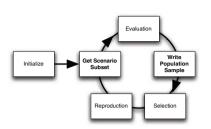

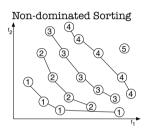

| <b>Peter van Stralen, Andy Pimentel</b><br>Fast Scenario-Based Design Space Exploration using Feature Selection                                                                                                          | 397 |

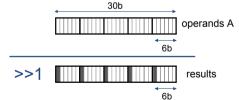

| Georgia Psychou, Robert Fasthuber, Jos Hulzink, Jos Huisken,<br>Francky Catthoor<br>Sub-word Handling in Data-parallel Mapping                                                                                           | 409 |

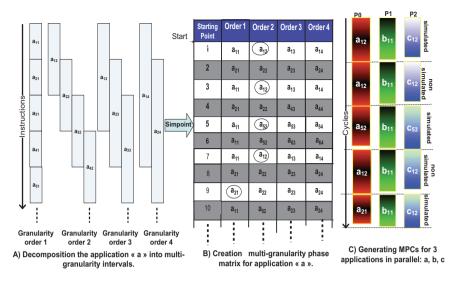

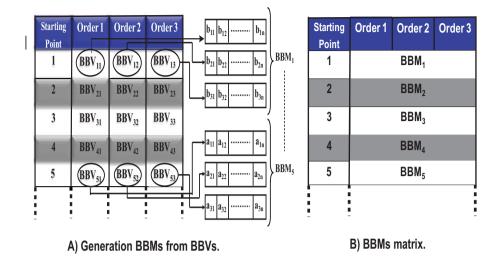

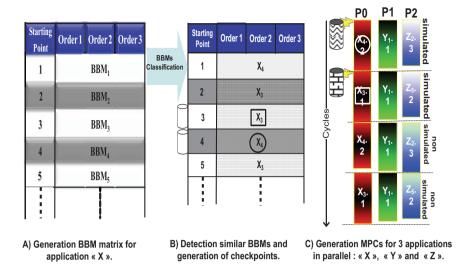

| Melhem Tawk, Khaled Z. Ibrahim, Smail Niar<br>Concurrent Phase Classification for Accelerating MPSoC Simulation                                                                                                          | 409 |

| David Neuhäuser, Eberhard Zehendner                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resilient data encoding for fault-prone signal transmission in parallelized signed-digit based arithmetic                                                                                                       |

| <b>Peter Sobe</b><br>Parallel coding for storage systems – An OpenMP and OpenCL capable<br>framework                                                                                                            |

| <b>Steffen Schiele, Holger Blaar, Detlef Thürkow, Markus Möller,</b><br><b>Matthias Müller-Hanneman</b><br>Parallelization Strategies to Speed-Up Computations for Terrain Analysis on<br>Multi-Core Processors |

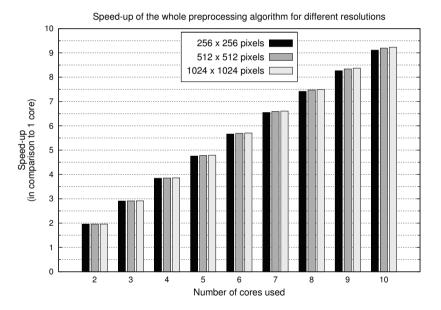

| <b>Dominik Schoenwetter, Max Schneider, Dietmar Fey</b><br>A Speed-Up Study for a Parallelized White Light Interferometry<br>Preprocessing Algorithm on a Virtual Embedded Multiprocessor System                |

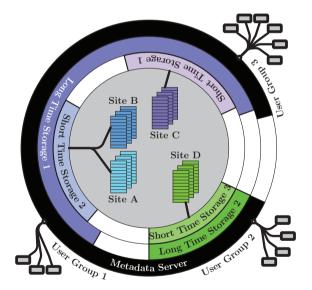

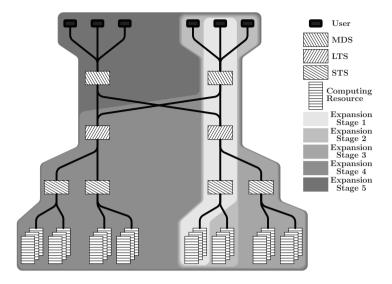

| Marcus Hilbrich, Ralph Müller-Pfefferkorn<br>Achieving scalability for job centric monitoring in a distributed infrastructure                                                                                   |

| <b>Deepak Ajwani, Andreas Beckmann, Ulrich Meyer, David Veith</b><br>I/O-efficient approximation of graph diameters by parallel cluster growing – a first experimental study                                    |

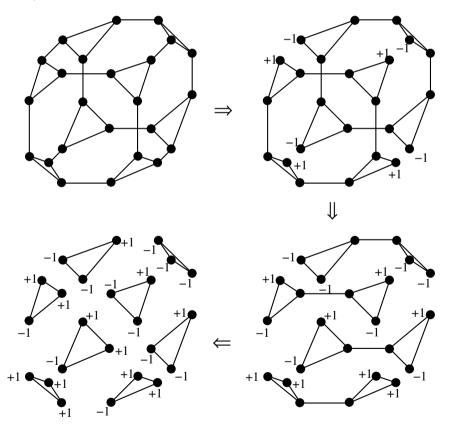

| <b>Christian Riess, Volker Strehl, Rolf Wanka</b><br><i>The Spectral Relation between the Cube-Connected Cycles and the</i><br><i>Shuffle-Exchange Network</i>                                                  |

| <b>Christoph W. Kessler, Erik Hansson</b><br><i>Flexible Scheduling and Thread Allocation for Synchronous Parallel Tasks</i>                                                                                    |

10th Workshop on Parallel Systems and Algorithms

## **ASPRIT 2012**

## Workshop on Architectures for Self-Organizing Private IT-Spheres

organized by

Detlef Krömker, Johann Wolfgang Goethe-Universität, Germany Ralf Dörner, Hochschule RheinMain, Germany Uwe Brinkschulte, Johann Wolfgang Goethe-Universität, Germany

## **QoS-based Testing and Selection of Semantic Services**

Jan Schaefer Reinhold Kroeger Design Computer Science Media Department RheinMain University of Applied Sciences Wiesbaden, Germany {jan.schaefer|reinhold.kroeger}@hs-rm.de

Simone Meixler Uwe Brinkschulte Department of Computer Science Johann Wolfgang Goethe University Frankfurt am Main, Germany {meixler|brinks}@es.cs.uni-frankfurt.de

#### Abstract:

The importance of context-awareness is constantly increasing. Users want systems to react dynamically to their current context (e.g. their location). For emerging home service platforms, this represents a key element, as it allows systems to increase the users' comfort tremendously by acting on sensed and deducted situations. As such systems feature a lot of dynamic interaction between services, it has to be ensured that service selections and bindings simply *work*. This paper proposes an approach for QoS-based testing and selection of semantic services, which employs a service tester that uses genetic algorithms to check and monitor QoS properties. These properties are used to complete the semantic descriptions of services running on the platform, which are managed by a semantic service registry.

## 1 Introduction

The increasing amount of IT hardware and software (e.g. "apps") in personal living spaces allows users to experience more and more services both online via the Internet and offline in their homes: personal computers, smartphones, tablets, home theater devices and smart homes are becoming more and more intertwined with each other and online services (Internet and/or cloud services) forming an *Ambient Assisted Living* (AAL) home service platform. The term *Ambient Assisted Living* (AAL) was coined by the European Commission's Information Society in 2004, as AAL research activities were prepared in a special support action project that was part of the 6<sup>th</sup> European Framework Programme [Gmb04]. AAL-related technologies introduce a complexity that users can or do not want to administrate themselves anymore. The increase of networked electronics and software can be compared to the increase of assistive and media technologies in cars during the last two decades. Unlike in cars, however, personal electronic devices and applications are much more open to (deliberate) modifications and data exchange, which makes securing their handling even more difficult. Finding and selecting the right service when using this home service platform can become a time-consuming and even dangerous process (from an IT security perspective), if there are multiple service providers and a malicious or malfunctioning service is selected. In addition, usually multiple applications are active in parallel requiring binding decisions almost constantly.

Static binding between client consumer and provider, which usually takes place once at the application's compile/link time, is not a feasible approach here. Even dynamic binding with its implementation-dependent, tight coupling between consumer and provider is not sufficient. As smart homes consist of heterogeneous, distributed systems with varying computation capabilities, they represent an ideal environment for service-oriented computing with its loose coupling thus supporting the required runtime dynamics, which explains the advent and propagation of home service platforms in general. However, the service interface descriptions and, even more importantly, any existing service properties offered by service providers (typically name-value pairs) are still statically defined, as they do not reflect the runtime state of the provided implementations. This results in syntactic service look-ups, in which the binding only depends on the service interface and its statically defined properties. To support the definition of extended and dynamic service descriptions that are integrated with a common context model – an ontology – for the platform, the ability to define and process semantics is needed. The approach presented here allows clients to define semantic queries for services, which can be processed by the service platform. As these queries can use the semantics of both services and platform, it is possible to build adaptive, context-aware applications, in which clients can react to changing service and context properties, as service properties reflect the runtime state of the platform and its components.

With respect to the functional properties a service defines (e.g. regarding its input and output parameters), clients (i.e., users or applications) might require non-functional service capabilities such as *Quality of Service* (QoS) properties. In this case, the clients' needs can be formulated explicitly or as part of their preferences. Service properties, on the other hand, are typically either defined statically or dynamically gathered at runtime (e.g. by application instrumentation). The first approach is both hard to achieve and insufficient as it doesn't reflect the user experience: a service might be fast if accessed in one geographic region but slow in another. The second approach, however, might also be inapplicable as ongoing runtime instrumentation might lower the service's performance too much impairing end user experience. This paper proposes a third approach: The integration of semantic service descriptions with service testing and probing capabilities. Here, service implementations register a test interface, which is used to determine runtime QoS properties, before the service is used for the first time. The resulting QoS properties become part of the service's description and can be used either for service look-up or selection of the fittest service if multiple services fulfill the client's requirements. The subsequent service probing adapts automatically to the currently offered services as well as to the usage of these services. We also consider to keep the testing effort within reasonable bounds.

This paper is structured as follows: Section 2 presents required background information and is followed by Section 3, which presents related approaches. The subsequent Section 4 introduces the approach for QoS-based testing and selection of semantic services. Section 5 discusses the current state of and the next steps for the work presented here.

## 2 Background

## 2.1 The Web Ontology Language

The W3C specification for the *Web Ontology Language* (OWL) [Gro09] defines a family of languages to support the *Semantic Web* vision. While RDF already allows addressing resources and their properties via URIs thus creating a formal, triple-based representation of information, OWL adds machine-processable semantics enabling automated interpretation of this information by computers. Furthermore, OWL supports an inference mechanism – so-called *reasoning* – that allows the automated derivation of new information from existing descriptions of things and their relationships. To support reasoning and limit its complexity, which leads to increasing processing times, the OWL specification defines three OWL sublanguages with different levels of expressiveness: *OWL Lite, OWL DL* (includes Lite) and *OWL Full* (includes DL), where OWL DL was designed to provide maximum expressiveness while retaining computational completeness. Apart from these sublanguages, the OWL specification also supports several exchange syntaxes for specification and exchange purposes with varying degrees of human readability.

An OWL ontology contains statements consisting of *Resource-Property-Value* triples (e.g. *Father hasName 'John'*). A resource has a *Class* definition and features a number of *Indi-viduals*, which represent the actual objects in a domain. Properties may feature *Domains* and *Ranges*: *Data Properties* associate resources with constants, whereas *Object Properties* associate resources with each other. In addition, properties may possess more detailed logical capabilities such as being functional, transitive, symmetric, reflexive, inverse and/or disjoint.

## 2.2 Genetic Algorithms

Genetic Algorithms are used for solving optimization problems and are based on the biological evolution theory. Terms that are often used for genetic algorithms are listed in table 1. Furthermore, the table shows the biological and IT specific translation of these terms.

| Term       | <b>Biological Translation</b> | IT Translation                                |  |

|------------|-------------------------------|-----------------------------------------------|--|

| Population | Set of individuals            | Set of solution candidates                    |  |

| Parents    | Mating subset of population   | Selected individuals for generating new solu- |  |

|            |                               | tion candidates                               |  |

| Fitness    | Conformity of an individual   | Quality of candidate solution                 |  |

| Chromosom  | Properties of a individual    | String                                        |  |

| Gen        | Part of a Chromosom           | char                                          |  |

| Allele     | Characteristic of a gen       | value of char                                 |  |

| Locus      | Location of a gen             | Position of a char                            |  |

#### Table 1: Genetic terms

From random variation new advantageous properties develop and will establish oneself in

the current environment. As the environment changes, properties can become disadvantageous. They may get replaced by properties that better fit to the current environment. For generating new solutions, genetic operators are used. Before using a genetic operator, individuals have to be selected. There exist many different types of selection methods. Fitness proportionate selection also called roulette-wheel selection is used as basis for our selection method, which is introduced in Section 4.4. After selecting two individuals, the genetic crossover operator can be used. Furthermore, random variation can be accomplished with the mutation operator. After creating the new population, the mutation operator can be used to choose randomly an allele and change its value. The reproduction operator is used to take individuals unchanged into the next generation. For the testing method, we have developed specific crossover, mutation and reproduction operators. A detailed explanation of these newly defined operators can be found in Section 4.4.

## 3 Related Work

With maturing tool support and increasing processing power, semantic (context-aware) services have gained enormous interest in recent years. Several approaches to semantics definition have been developed and compared in the last decade [CDM<sup>+</sup>04, ZKN06]. However, OWL-S, the *Semantic Markup for Web Services* extension for OWL, which provides additional concepts for specifying semantic processes and services, remains the one most widely used today, although it focuses on Web services environments. Due to its modularity, however, it allows the definition of *Service Groundings* for other service architectures.

Even before semantic services were examined in particular, several context modeling approaches for home service platforms emerged. Gu, Pung, Zhang [GPZ04] propose using layered ontologies for context models in the home domain. It covers widely-acknowledged concepts that also appear in more recent publications (e.g. activities, locations, persons, devices including a custom service concept). However, the interaction of formal service definitions with runtime systems (actual groundings) and how user preferences influence the platform's behavior are not discussed. Daz Redondo et al.  $[RVC^+08]$  propose the combination of OWL-S with an OSGi grounding called OWL-OS, although neither QoS properties nor semantic queries for service selection are supported (only key-value pairs). However, the authors use OWL-S service categories as a means to group services into aspects (e.g. Lighting), which can be used by clients during service look-up. Romero et al. [RHT<sup>+</sup>11] propose a platform based on the Service Component Architecture (SCA), which provides similar service and component abstractions as OSGi. The paper focuses on device integration over heterogeneous communication protocols into an event processing architecture, which is able to process data from a wide collection of devices (including sensor networks). However, a semantic abstractions for implementation details and support for the deployment of additional (3rd party) services are not presented.

Apart from home service platforms, a broad collection of service discovery and binding approaches have been developed in the past. The most widely used specifications for this today, especially in living environments, is *Universal Plug and Play* (UPnP) [UPn11].

Apart from its convincing technical capabilities, it lacks OWL's modeling capabilities as well as support for rules, queries and reasoning. Thus, it rather can be seen as a potential grounding for OWL-S services.

## 4 Approach

The work presented here proposes enhancements to home service platforms, which allow extending, testing and integrating the collection of applications and services dynamically based on semantic descriptions of service properties.

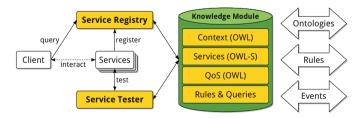

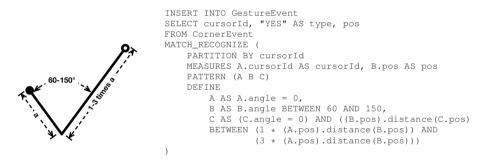

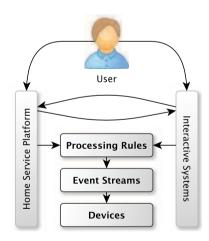

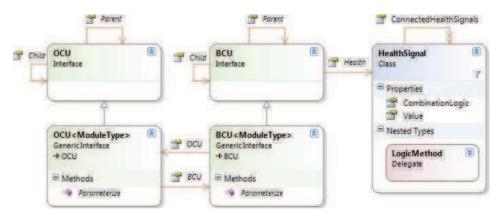

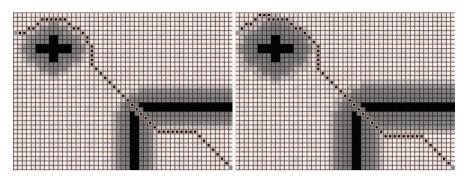

## 4.1 A Platform for Semantic Services

The approach presented here proposes adding semantic interfaces and continuous testing to applications and services that integrate with common OWL ontologies provided by a *Semantic Service Registry*. This registry allows extending an existing service registry for non-semantic services by adding the capability to manage ontologies and supporting semantic service queries. This extension supports the installation of non-semantic and semantic services in parallel. An overview of the surrounding platform is given in [Sch10]. In addition, the *Service Tester* component uses the descriptions of registered services to gather runtime QoS properties once after service registration. After that, the Service Tester is able to probe services on demand. The *Knowledge Module* stores the context and application ontologies including related rules, which are accessed by the other components. With changing system context, the contained ontologies are updated by incoming events resulting in constantly changing facts and, thus, also changing service properties. This dynamic can be used by clients in service look-ups, as bound services can differ between two subsequent look-ups due to interim model changes (e.g. state, location or performance change). The interaction between the involved components is displayed in Figure 1.

Figure 1: Service Registration and Testing

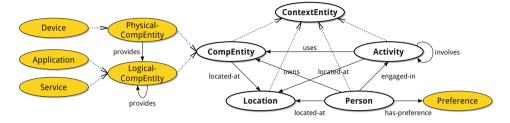

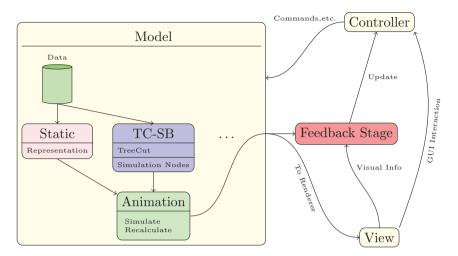

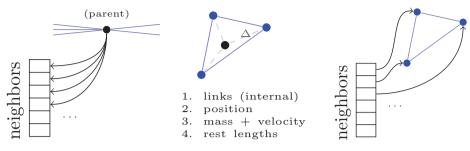

The context model has been constructed around the core concepts *Person*, *Computational Entitiy*, *Location* and *Activity* and is based on the context model from Gu et al. [GPZ04] introduced in Section 3, which has been extended with more detailed concepts for computational entities, services, activities and user preferences (among others) for this approach,

although the latter two are not covered here. Figure 2 presents a condensed version of the context model, in which the colored shapes represent some of the additions to the original model. The service-related ontologies contain service descriptions from service groundings (implementations) to formal service models and are defined using OWL-S. The *Service Registry* is responsible for registering and looking up services in the knowledge module and the platform's registry mechanism.

Figure 2: Context Model (condensed)

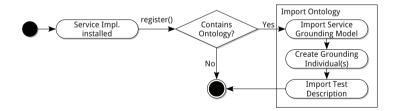

#### 4.2 Service Registration

If a service implementation is installed by a service provider, it registers its implementation details – the service grounding – with the service registry assuming that the ontology describing the implementation integrates with the context and service ontologies. Subsequently, this integration allows the registry to find the service implementation, if the associated service is looked-up.

Figure 3: Service Registration Process

Apart from functional service properties (interfaces and parameters), services register additional context-related or QoS-related properties that can be specified as requirements by clients during service look-up. If these properties are dynamic, they are updated by the registry at runtime (e.g. by testing as described in Section 4.4). The registry is also responsible for removing service groundings, if service implementations are uninstalled or unavailable (e.g. caused by service failures). It is also possible for clients or services to register and update context or service ontologies without providing an implementation for them, as ontologies and implementations are decoupled.

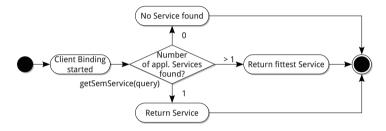

#### 4.3 Service Selection

If clients require a service, they can query the service registry for implementations of that service. This can be done using the platform's own service selection approach (if one exists), or by executing *SPARQL* queries [PE08] on the semantic service registry. The latter approach is required, if semantic properties are used for the service look-up. For the definition of look-ups, clients can use both functional and non-functional properties resulting in comprehensive queries. This can lead to situations, in which no service is able to meet these requirements. However, typically clients only define a limited set of requirements and end up with a selection of functionally equal services. In this case, the registry relies on the results of the service tests to select the fittest service. The service selection process is shown in Figure 4.

Figure 4: Service Selection Process

As an example, a client might look for a service providing off-site health monitoring. Here, services might feature more or less static properties such as the service provider's general trustability or service cost. Properties such as availability or response time, on the other hand, are dynamic properties, which would be collected by the service tester.

#### 4.4 Service Testing

Given the new situation of being able to dynamically extend the service platform by services from different providers results in a great responsibility for testing these services. The need of testing is rooted in the fact that services can be added, deleted or substituted. Therefore no proven information exists how they perform on given client requests. As services of different service provider are supposed to interact, it is necessary to be able to rely on information given for these services (for example QoS Properties). Hence, a testing method should fulfill the requirements of adapting to currently offered services and client requests as well as being independent from the service provider offering a service. Therefore, we combine the approach of using a knowledge module with the approach of using genetic algorithms [MB10] for creating test sets.

| QoS Property  | Category | Valid Values |

|---------------|----------|--------------|

| Response Time | 1        | $\leq 5ms$   |

|               | 2        | 6ms - 10ms   |

|               | 3        | 11ms-20ms    |

|               | 4        | $\geq 21ms$  |

Table 2: Category Example

#### 4.4.1 Test Case Adaption

In the following, a test set denotes a number of l different test cases. It should be taken care that a test set does not contain too many test cases because every test case results in a service-request and every service-request generates load for the service provider system. Therefore, it is necessary to find a suitable selection of test cases to compare and test services. As suggested in [Xia06], test cases are categorized by QoS properties and quality levels. Therefore, every QoS property is divided into different quality categories on the test system. These categories are used to distinguish between different QoS requirements. The test system manages m test sets for one category. A QoS property is e.g. the response time. Table 2 shows an example for such response time categories.

| Crossover Oper-<br>ator                          | Modified<br>Crossover<br>Operator |  |

|--------------------------------------------------|-----------------------------------|--|

| Two offspring                                    | One offspring                     |  |

| Locus of a gen is                                | Locus of a gen is                 |  |

| important                                        | not important                     |  |

| All alleles are<br>handed on to the<br>offspring |                                   |  |

Table 3: Crossover Operator Modifications

If a client discovers a non-functional error, he has to send the ID of the service causing this error to the test system, the corresponding input, and the violated requirements. The test system uses these errors as test cases and generates test sets with this information. An error counter is attached to every test case. The value of the error counter reflects the up-to-dateness of a test case. When an error is reported, the corresponding error counter will be increased. In case of a new error, a test set will be chosen randomly and a test case to be substituted will be selected. For the selection,

it has to be checked if the test set contains test cases having an error counter of value zero. In this case, one of them will be chosen randomly to be substituted. Otherwise, the selection of a test case will be based on a probability reverse proportional to its error counter. Test sets cannot be generated by errors only, but also by recombination of existing test sets. The advantage of recombinations is that good test cases can be unified to one test set. Hereby, is it possible to create better test sets from already existing ones. The approach presented in this paper is based on a genetic algorithm. This algorithm shows differences to standard genetic algorithms to reflect the considered application. Individuals are given by test sets of a QoS property category.

Test cases form the alleles and the fitness of a test set (individual).  $t_j$  is denoted as  $f(t_j)$  and equals the sum of the error counters belonging to test cases of  $t_j$ . Let  $ec_i$  be the

error counter of test case *i*. Using the fitness, we can calculate the probabilities of the individuals. The probability  $p_j$  of an individual *j* depicts its possibility to survive, because an individual is chosen for the reproduction operator as well as for the crossover operator

with probability

$$p_j = \frac{f(t_j)}{F}$$

, where  $f(t_j) = \sum_{i=1}^{l} ec_i$  and  $F = \sum_{j=1}^{l} f(t_j)$

For the crossover operator, two individuals have to be chosen. The crossover operator will produce one offspring from these two individuals. Not all alleles will be handed to the offspring, it will be distinguished between dominant and recessive alleles. The selection of alleles, which will be part of the subsequent generation, is affected by the probabilities calculated based on the error counters. The probability to include a test case (allele) in the next generation is proportional to the value of its error counter. First of all, the sum S of all error counters for both test sets has to be provided to calculate the probability  $S = \sum_{j=1}^{2} \sum_{i=1}^{l} ec_{ij}$ , where  $ec_{ij}$  is the error counter of test case i in test set j. Afterwards, the probability  $p_{ij}^C = \frac{ec_{ij}}{S}$  can be calculated. Because we do not put back a selected allele, the values of S and  $p_{ij}^C$  change after every selection. Test cases handed on to the next generation by the crossover operator are called *dominant* alleles while the others are called *recessive*. Changes made to the crossover operator compared to the standard

The reproduction operator moves an individual to the next generation without any changes. The only modification of this operator is not to allow an individual to be cho-

crossover operator are listed in Table 3.

tion without any changes. The only modification of this operator is not to allow an individual to be chosen twice. Therefore the value of F as well as  $p_j$  change after every selection. A major problem of the crossover and reproduction operator is their seldom appliance to test sets having a low fitness value. Even with this low fitness value, these test sets might contain some test cases with high error counter values. Due to low error counter values of the majority of test cases,

| Mutation Operator                                    | Modified Mutation<br>Operator                                                                          |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Random selection of an allele which is to be mutated | The probability of se-<br>lecting an allele to be<br>mutated depends on its<br>error counter           |

| New allele is chosen randomly                        | New allele is chosen<br>from parent generation<br>with the help of the Fit-<br>ness and error counters |

| Mutation is not can-<br>celled                       | Mutation will be can-<br>celled if it causes a du-<br>plicate allele                                   |

Table 4: Mutation Operator Modifications

the overall sum nevertheless would be low. These high rated test cases would rarely have a chance to be handed on to the next generation without the mutation operator. For every mutation a test set has to be chosen from the current generation. The selection of test set j from all available test sets is done with probability  $p_j^M = 1 - p_j$ , where  $p_j$  is defined as described before. A test set is chosen for mutation with a probability reverse proportional to its fitness. This allows to extract test cases with high error counter values from test sets with a low fitness. From the chosen test set, a test case  $s_i$  will be taken with the probability  $p_i^{MST}$ . This probability is proportional to the value of the corresponding error counter  $ec_i$  of test case  $s_i : p_i^{MST} = \frac{ec_i}{\sum\limits_{j=1}^{l} ec_j}$ . A test case  $e_k$  from the next generation has to be chosen

to be substituted by test case  $s_i$ . The test set in which the substitution takes place is chosen randomly. If the test case  $s_i$  is already an element of this test set, the mutation will be cancelled. This avoids the presence of duplicate test cases in a test set. Test case  $e_k$ , which has to be substituted, will be chosen with probability  $p_k^{MET} = 1 - \frac{ec_k}{\sum\limits_{j=1}^{l} ec_j}$ . This results

in test cases with a low error counter having a higher probability to be substituted. The modifications of the mutation operator are summarized in Table 4.

Genetics provide a solution for adaption of individuals to a changing environment. This is one reason for taking genetic algorithms to address the issue of test case adaption. Another important issue is that genetics only takes the sum of all properties of an individual to calculate its fitness. This means an individual having a high fitness may even have low rated properties. The importance of handing on properties with a low rating is given by the changing environment. The rating of a property can improve as the system context changes. This reflects the changing ability of test cases to detect faults as the offered services and the requests change. We are confronted with the problem of an always changing search space and the consequence of never reaching a final optimum. The goal is to keep a variety of test cases and also to consider their rating changes over time. This implies giving newly registered test cases a chance to improve. Therefore, test cases with a low error counter should also get a chance to be integrated into the used test set.

#### 4.4.2 Initial Test Setup

Initially, no test sets exist. However, services have to be tested from the start to find out which requirements they fulfill. Therefore, this phase will be conducted similarly to  $[TPC^+03]$ . When a service is registered to the test system, the service provider has to deliver test cases for this service. Furthermore, the service provider has to deliver information about the service's QoS properties. Optionally, the service provider can specify, for which QoS property a test case is especially applicable. If no information is given, the test case will be seen as relevant for all QoS properties. The QoS property category of a test case is given by the QoS properties of the corresponding service. These initial test cases will be put into a pool belonging to the corresponding QoS property and category. There is a dedicated pool for every type of service and QoS property category. Furthermore, the pool can have test cases sent by a client. These test cases might not have caused any errors yet, but the client favors them to be tested. In this case, the client has to act like a service provider. The client has to send the type of service to be tested, the QoS property and the QoS property category. This enables testing a service not only with its own provided test cases, but also with other test cases provided by services of the same category or by clients.

The *m* test sets are generated with randomly chosen test cases from the corresponding pool. Test cases are removed from the pool as soon as they are used in a test set. As an improvement to the work of  $[TPC^+03]$ , services are also tested with inputs, which are currently used by clients and already have caused errors.

The step of generating a pool and m test sets is only necessary, if a service of a not existing functional domain is registered. Errors and inputs can be reported continuously to the service registry. Furthermore, the adaption and testing is a continuously repeating process of our test system.

## 5 Current State and Outlook

The approach presented in this paper is part of ongoing research, which focuses on enhancing the (self-)management capabilities of emerging home service platforms. Although the context model and the semantic service extensions presented here are fundamental elements of context-aware systems, they are just the basics for the creation of these selfmanagement capabilities. As the introduction of semantics, just like service-orientation, decouple concepts from implementation technologies, the semantic service registry concept presented here is not limited to a specific implementation technology. For the prototypical implementation, however, the OSGi service platform [OSG09] was selected in combination with the Jena Semantic Web Framework [jen08] and the Pellet OWL 2 Reasoner [SPG<sup>+</sup>07] for ontology and SPARQL query processing. Here, the semantic service registry extends the default OSGi service registry and offers an additional client API for semantic service selection. Service registrations use either distinct or default OSGi API methods. In the case of the latter, OSGi service registration calls are intercepted and their associated bundles inspected for ontologies using OSGi's Event Hook mechanism that allows the inspection of OSGi services, whenever their runtime state changes (i.e., they are registered or unregistered). As clients have to formulate specific queries for semantic service look-ups, the semantic API offers an additional query-based method for this. At the current stage, however, the client still has to address the OSGi service interface of the targeted semantic service as part of the invocation, as abstract service queries including parameters cannot be mapped to arbitrary OSGi services currently, yet. For goalor intention-driven semantic services, the service semantics have to be decoupled from service interfaces as well.

Part of this research focuses on the development of a self-management module for service platforms, which relies on dedicated management ontologies and associated rules to manage the platform – applications, services and devices – autonomically. As monitoring and state assessment are critical for this task, this management module relies on sensors and tests (as described in Section 4.4) to gather runtime information required to compute an appropriate management action to improve the managed system's state. Here, the approach for service testing with test sets plays an important role, as the effectiveness of management actions could be tested in this setup as well. Apart from the self-management module, test sets, which adapt to the current faults and offered services. The advantages of this testing method, therefore, lie in dynamic service environments. Future work will implement, test, and compare this approach with other solutions. Furthermore we think about expanding the fitness function to include other parameters besides the error counter.

#### References

- [CDM<sup>+</sup>04] Liliana Cabral, John Domingue, Enrico Motta, Terry R. Payne, and Farshad Hakimpour. Approaches to Semantic Web Services: An Overview and Comparison. In *European Semantic Web Conference*, May 2004.

- [Gmb04] VDI/VDE Innovation + Technik GmbH. Ambient Assisted Living Preparation of an Article 169 Initiative. http://http://www.aal169.org, September 2004.

- [GPZ04] T. Gu, H.K. Pung, and D.Q. Zhang. Toward an OSGi-based infrastructure for contextaware applications. *Pervasive Computing, IEEE*, 3(4):66 – 74, Oct.-Dec. 2004.

- [Gro09] W3C OWL Working Group. OWL 2 Web Ontology Language Document Overview (W3C Recommendation). http://www.w3.org/TR/owl2-overview/, October 2009.

- [jen08] Jena Semantic Web Framework for Java. http://openjena.org, January 2008.

- [MB10] Simone Meixler and Uwe Brinkschulte. Test Case Generation for Non-functional and Functional Testing of Services. *Object-Oriented Real-Time Distributed Computing, IEEE International Symposium on*, pages 245–249, 2010.

- [OSG09] OSGi Alliance. OSGi Service Platform Release 4 (Version 4.2) Core Specification. http://www.osgi.org/Download/Release4V42/, May 2009.

- [PE08] Eric Prud'hommeaux and Andy Seaborne (Editors). SPARQL Query Language for RDF (W3C Recommendation). http://www.w3.org/TR/ rdf-sparql-query/, January 2008.

- [RHT<sup>+</sup>11] Daniel Romero, Gabriel Hermosillo, Amirhosein Taherkordi, Russel Nzekwa, Romain Rouvoy, and Frank Eliassen. The DigiHome Service-Oriented Platform. Software: Practice and Experience, 2011.

- [RVC<sup>+</sup>08] R.P. Diaz Redondo, A.F. Vilas, M.R. Cabrer, J.J.P. Arias, J.G. Duque, and A.G. Solla. Enhancing Residential Gateways: A Semantic OSGi Platform. *Intelligent Systems, IEEE*, 23(1):32–40, Jan.-Feb. 2008.

- [Sch10] Jan Schaefer. A Middleware for Self-Organising Distributed Ambient Assisted Living Applications. In *Workshop Selbstorganisierende, Adaptive, Kontextsensitive verteilte Systeme (SAKS)*, March 2010.

- [SPG<sup>+</sup>07] Evren Sirin, Bijan Parsia, Bernardo Cuenca Grau, Aditya Kalyanpur, and Yarden Katz. Pellet: A Practical OWL-DL Reasoner. *Web Semant.*, 5:51–53, June 2007.

- [TPC<sup>+</sup>03] W. T. Tsai, R. Paul, Z. Cao, L. Yu, A. Saimi, and B. Xiao. Verification of web services using an enhanced uddi server. *Object-Oriented Real-Time Dependable Systems, IEEE International Workshop on*, 0:131, 2003.

- [UPn11] UPnP Forum. About UPnP Forum. http://upnp.org/about/, August 2011.

- [Xia06] Jinchun Xia. Qos-based service composition. In COMPSAC '06: Proceedings of the 30th Annual International Computer Software and Applications Conference, pages 359–361, Washington, DC, USA, 2006. IEEE Computer Society.

- [ZKN06] Jiehan Zhou, J.-P. Koivisto, and E. Niemela. A Survey on Semantic Web Services and a Case Study. In Computer Supported Cooperative Work in Design, 2006. CSCWD '06. 10th International Conference on, pages 1 –7, May 2006.

## Adaptive Content Distribution Network for Live and On-Demand Streaming

Yuta Miyauchi, Noriko Matsumoto, Norihiko Yoshida

Graduate School of Science and Engineering Saitama University Saitama 338-8570, Japan {yuta, noriko, yoshida}@ss.ics.saitama-u.ac.jp

Yuko Kamiya, Toshihiko Shimokawa

Graduate School of Information Science Kyushu Sangyo University Fukuoka 813-8503, Japan {kamiya, toshi}@nw.is.kyusan-u.ac.jp

**Abstract:** We have proposed an adaptive content distribution network (CDN), FCAN (Flash Crowds Alleviation Network), which changes its structure dynamically against *a flash crowd*, that is a rapid increase in server load caused by a sudden access concentration. FCAN in our preceding studies responds only to static content delivery. In this paper, we extend FCAN to alleviate flash crowds in video streaming. Through some experiments, we confirmed that FCAN for video streaming is effective to alleviate flash crowds.

## 1 Introduction

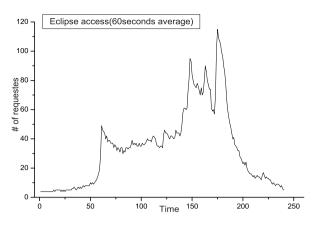

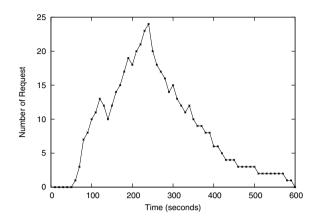

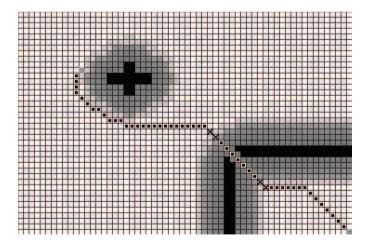

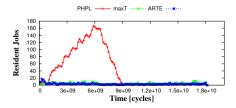

When a Web site catches the attention of a large number of people, it gets an unexpected and overwhelming surge in traffic, usually causing network saturation and server malfunction, and consequently making the site temporarily unreachable. This is the "flash crowd" phenomenon on the Internet. An example of a flash crowd is Figure 1, which shows the traffic volume of Web site during the solar eclipse based on a real access log provided from "LIVE! ECLIPSE 2006" [LE06]. During the solar eclipse, the accesses from clients increased several times higher than the normal condition by flash crowds.

We have proposed an adaptive content distribution network (CDN), FCAN (Flash Crowds Alleviation Network), which changes its network structure adaptively depending on a load fluctuation against flash crowds [Pan06, Yos08]. FCAN only focused on static content delivery in our preceding studies, thus in this study, we extend FCAN to video streaming.

A large amount of clients receive a sequential stream from a streaming server, therefore network traffic is concentrated on a specific site on the Internet. To assure resilience in

Figure 1: Flash Crowds on "LIVE! ECLIPSE 2006" site

P2P video streaming, the FCAN framework is thought to be promising. There is a survey paper on resilience in P2P video streaming [Abb11], however, there is no system which changes its network structure dynamically according to load fluctuation.

In this paper, we describe FCAN's extension. It uses Apple's HTTP Live Streaming [AD11a] for stream segmentation and distributed delivery. This paper is organized as follows: Section 2 provides a brief overview of HTTP Live Streaming. Section 3 presents an overview of our previous FCAN for static content delivery. Section 4 gives FCAN's extending design for video streaming. Section 5 describes preliminary experiments with a simple prototype. Section 6 contains some concluding remarks.

## 2 HTTP Live Streaming

Conventional standard streaming protocols such as progressive download and real-time streaming do not allow switching of stream source servers on the client side dynamically. Therefore, massive accesses from clients concentrates on a particular site on the Internet. Accordingly, the server and its surrounding network choke up, and a flash crowd occurs.

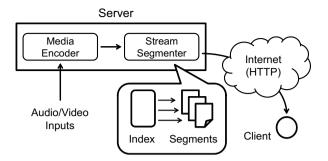

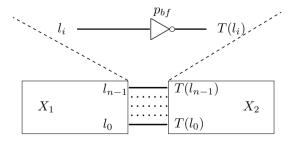

In order to resolve this problem of conventional protocols, Apple has introduced a new protocol for video streaming, HTTP Live Streaming (also known as "HLS"). It has been proposed as a standard draft for the Internet Engineering Task Force [Pan11]. Figure 2 shows an overview of this protocol.

The server starts providing a video stream with the following procedure: (1) Encodes an audio/video inputs; (2) Divides the encoded stream into a set of media segments (".ts" files), and makes an index (".M3U8" file) which refers them; (3) Delivers them to clients using HTTP on the Internet.

This protocol enable a client to switch the source server dynamically as opposed to the

Figure 2: HTTP Live Streaming Overview

conventional streaming protocols. The delivery system archives load distribution easily with additional servers.

As another key feature, HTTP Live Streaming supports "adaptive bitrate." The server provides alternative streams with different quality levels of bandwidths, so as to enable a client to optimize the video quality according to the network situation, as the load on the network and CPU, both on the server side and the client side, fluctuates on a frequent basis.

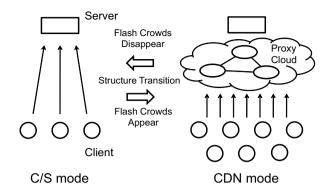

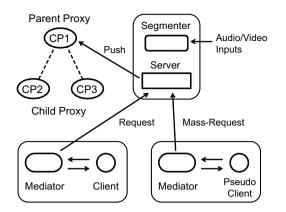

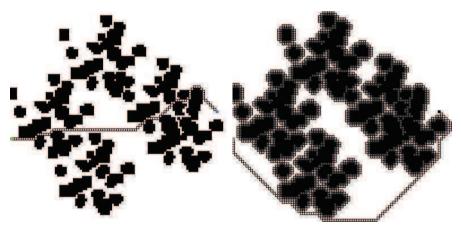

## 3 FCAN

FCAN is an adaptive CDN which takes the form of C/S or CDN depending on the amount of accesses from clients. Specifically, in the C/S mode, a server provides contents to clients as in a traditional C/S. In the CDN mode, when the server detects a coming of a flash crowd, volunteer cache proxies in the Internet construct a temporary P2P network and provide the content on behalf of the server. These volunteer proxies are recruited in advance out of providers and organizations. In case servers in such providers and organizations suffer from flash crowds, they will be helped by other volunteer proxies. FCAN is built upon this mutually-aiding policy. Figure 3 shows an overview of FCAN.

In our preceding studies, we summarized some researches to alleviate flash crowds [Yos08]. These researches are divided into three categories: server-layer, inter-mediatelayer and client-layer solutions, according to typical architectures of networks. FCAN is an intermediate-layer solution, which employs an Internet infrastructure of cache proxies to organize a temporal P2P-based proxy cloud for load balancing. However, FCAN has some extensions with some dynamic and adaptive features. Our FCAN studies achieved very promising results regarding static content delivery on the real Internet [Miy11].

Figure 3: FCAN Overview

## 4 FCAN for Streaming

#### 4.1 Structure Transition

First, We changed the behavior of structure transition in the previous FCAN design.

The server and the cache proxies in the proxy network always monitor the amount of accesses they receive from clients and evaluate the load on the network. The system switches to the CDN mode if all nodes' loads are higher than a certain threshold, and switches back to the C/S mode if lower. Each cache proxy sends its own load information to the server periodically, and the server determines whether to perform structure transition.

We use two thresholds to prevent "thrashing" between the two mode. The threshold for transition from the C/S mode to the CDN mode is set to higher than the one for transition from the CDN to C/S.

In peaceful times, the conventional C/S architecture satisfies most of the client requests. A server and cache proxies, both of which comprise FCAN, do little more than what normal ones do. When a flash crowd comes, the server detects the increase in traffic load. It triggers a subset of the proxies to form an overlay, through which all requests are conducted. All subsequent client requests are routed to this overlay.

The server-side procedure is outlined as follows: (1) Selects a subset of proxies to form a CDN-like overlay of surrogates, and builds a distribution tree; (2) Pushes the index file and stream segments to the node of the distribution tree, so as to meet the real-time constraint of the video streaming; (3) Prepares to collect and evaluate statistics for the object from the involved proxies, so as to determine dynamic reorganization and release of the overlay.

The proxy-side procedure is outlined as follows: (1) Changes its mode from a proxy to a surrogate (or, in the strict sense, a mixed mode of a forward proxy and a surrogate); (2) Stores flash-crowd objects (except the index file) permanently, which should not expire until the flash crowd is over; (3) Begins monitoring the statistics of request rate and load,

Figure 4: Handling of load increase in CDN mode

and reporting them to the server periodically.

In the live streaming, the index file is updated periodically, therefore the server monitors its composition, and pushes the segments at an appropriate time. Meanwhile, when the proxy is released by the server, it discards the index so as to keep the consistency among the nodes.

When the member server detects the leaving of the flash crowd, the involved proxies are dismissed one by one with the following procedure: (1) The server notifies the proxy to be dismissed; (2) The server requests the related proxies to modify the relation of connection; (3) The proxy changes its mode from a surrogate to a proxy.

The CDN-like overlay transits back to the normal C/S mode when all the proxies are dismissed. They are not all dismissed at once, since the low load may be just temporary, and the system should therefore remain in the anti-flash-crowd mode for a while.

## 4.2 Dynamic Resizing and Quality Restriction

The proxy network is a pure P2P network. Therefore, it is highly fault-tolerant and scalable. Unlike traditional P2P systems, it does not include clients into the network itself in order to assure reliability and security.

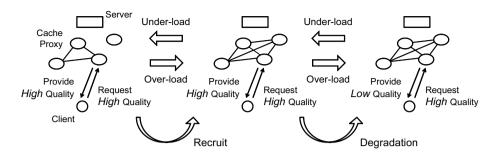

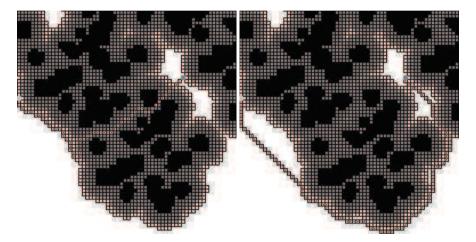

FCAN resizes a scale of the proxy network depending on a load fluctuation adaptively in order to avoid troubles such as server down by massive access concentration. Figure 4 shows how the system works in the CDN mode.

When the server detects a coming of flash crowds, it forms a temporary proxy network as shown in the lefthand side of Figure 4. If the initial network cannot handle increasing an amount of accesses, the server recruits a new member proxy one by one as shown in the middle of Figure 4.

If the server cannot recruit temporary proxies any more, it degrades the quality of the video stream as shown in the righthand side of Figure 4. For example, in the situation that the

system provides video streams of two different qualities, high and low, it delivers the low quality content as substitute for the high quality one under this quality restriction. The network occupancy per client decreases so that the server can alleviate the load of whole delivery network.

If the proxy network can easily handle all the incoming loads, the server may lift the restriction of the stream quality at first. After the derestriction, it releases temporarily-recruited proxies one by one until all proxies are dismissed. Finally, the system all turns back to the normal condition.

#### 4.3 Access Redirection

In our preceding studies, FCAN uses DNS-based redirection, i.e. the authoritative DNS server redirects an access to an appropriate node depending on the network structure. We use TENBIN [Shi00] for the authoritative DNS server. It is a high-performance DNS which allows server selection policies and DNS lookup entries to be changed dynamically. DNS-based redirection works transparently to users, however, we confirmed "cache effect" problem which is caused by some DNS servers somewhere in the world which make caches of the address resolution at their own discretion.

In this study, we make the client access redirect to an appropriate server through the *mediator*. The mediator works on the same machine as the client software and relays requests from the client to the servers. It handles client requests with the following procedure: (1) Receives a list of working servers from the origin server; (2) Receives the content from a certain server in the list, and provides it to the client; (3) When the mediator get a request from the client next time, it receives new list from a certain server; (4) Return to (2).

Using the mediator, we eliminate the cache effect problem, and even utilize geographical information-based redirection for example. While the mediator works non-transparently to users, we expect that the function of the mediator can be implemented in browser cookies in the future.

## **5** Preliminary Experiments

We conducted some preliminary experiments on a real network with a prototype of the system. Figure 5 shows an overview of the experiments.

In our experiments, we use some hosts in Saitama University and Kyushu Sangyo University for a server, proxies, a pseudo client, and a client node. We use Apple's stream segmenter (mediastreamsegmenter) for the segmenter, and QuickTime Player for QuickTime X in the client.

The pseudo client is to trigger the FCAN's functions against flash crowds. It submits requests for randomly chosen segments to the server following the pattern shown in the Figure 6. In the rest of this section, CP1, CP2 and CP3 are the proxies shown in the Figure

Figure 5: Experiment Environment

| Table 1: Segments for On-Demand Experiment |            |              |          |

|--------------------------------------------|------------|--------------|----------|

| Quality                                    | Resolution | Average size | Duration |

**m** 1 1

| Quality | Resolution       | Average size | Duration |

|---------|------------------|--------------|----------|

| High    | $480 \times 360$ | 960 [KB]     | 10 [sec] |

| Low     | $320 \times 240$ | 410 [KB]     | 10 [sec] |

#### 5.

We made two experiments with two delivery methods, live and on-demand. In the ondemand streaming experiment, the server provides high and low quality contents with adaptive bitrates. We use segments shown in Table 1, which are samples of HTTP Live Streaming in the Apple Developer's site [AD11b]. The client software, the client has a master index file indicating these two quality contents, and the QuickTime Player requests segments of an adequate quality depending on load fluctuation following the master index. On the other hand, in the live streaming experiment, the server provides contents in a single quality in real time.

The server computes a load value regarding the size of requested segments. In the experiments, thresholds for load detection are defined beforehand based on some experiences. Workloads on the real Internet varies, and automatic and dynamic configuration of the thresholds is difficult. We suppose they may be configured based on the server capacity and the network bandwidth around the server.

Table 2 shows the time-line of the live experiment. We confirmed that the structure transition and dynamic resizing were performed depending on load fluctuation.

Table 3 shows the time-line of the on-demand experiment. In addition to the result of the live streaming, the stream quality was limited during server load growth.

Table 4 shows the sequence of the stream segments which the client played in the ondemand experiment. The client consistently requested the high quality contents until the

Figure 6: Request Pattern of Pseudo Client

| Table 2: Time-line of Live Experiment |  |  |  |

|---------------------------------------|--|--|--|

| Actions                               |  |  |  |

| Start experiment                      |  |  |  |

| Pseudo client request start           |  |  |  |

| Client request start                  |  |  |  |

| Structure transition to CDN           |  |  |  |

| Recruit the core proxies (CP1, CP2)   |  |  |  |

| Recruit the additional proxy (CP3)    |  |  |  |

| Dismiss the additional proxy (CP3)    |  |  |  |

| Structure transition to C/S           |  |  |  |

| Dismiss the core proxies (CP1, CP2)   |  |  |  |

| End experiment                        |  |  |  |

|                                       |  |  |  |

Table 2: Time line of Live Experiment

end of the experiment. In the on-demand streaming, the segmentation is done before the beginning of the experiment and the composition of the index does not change, therefore, clients received some number of segments before playback. After the number 27, the server degraded the stream quality for load alleviation, so the client received low quality segments as substitutes for the high quality ones. As the server load decreased, the server lifted the restrictions on the quality. After the number 45, the client herewith received high quality segments as required again. During the experiment, no malfunctioning, such as interrupt in the playback, was observed when the quality changed.

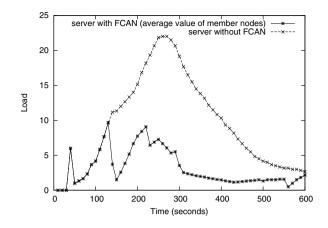

Figure 7 shows the load transitions of the server with FCAN and without FCAN in the on-demand experiment. The case of the server with FCAN shows the average loads of member nodes in the distribution network. The first peak at the 40th second shows that "buffering" was done when the client started the playback as mentioned above. The load on the server exceeded the higher threshold at the 130th second, then structure transition

| TimeActions0 [sec]Start experiment<br>Pseudo client request start30 [sec]Client request start30 [sec]Structure transition to CDN<br>Recruit the core proxies (CP1, CP2)220 [sec]Recruit the additional proxy (CP3)250 [sec]Quality degradation430 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/S<br>Dismiss the core proxies (CP1, CP2)600 [sec]End experiment | Table 3: Time-line of On-Demand Experiment |                                     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------|--|--|

| Pseudo client request start30 [sec]Client request start130 [sec]Structure transition to CDN<br>Recruit the core proxies (CP1, CP2)220 [sec]Recruit the additional proxy (CP3)250 [sec]Quality degradation430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/S<br>Dismiss the core proxies (CP1, CP2)                                 | Time                                       | Actions                             |  |  |

| 30 [sec]Client request start130 [sec]Structure transition to CDN<br>Recruit the core proxies (CP1, CP2)220 [sec]Recruit the additional proxy (CP3)250 [sec]Quality degradation430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/S<br>Dismiss the core proxies (CP1, CP2)                                                            | 0 [sec]                                    | Start experiment                    |  |  |

| 130 [sec]Structure transition to CDN<br>Recruit the core proxies (CP1, CP2)220 [sec]Recruit the additional proxy (CP3)250 [sec]Quality degradation430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/S<br>Dismiss the core proxies (CP1, CP2)                                                                                        |                                            | Pseudo client request start         |  |  |

| Recruit the core proxies (CP1, CP2)220 [sec]Recruit the additional proxy (CP3)250 [sec]Quality degradation430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/SDismiss the core proxies (CP1, CP2)                                                                                                                                    | 30 [sec]                                   | Client request start                |  |  |

| 220 [sec]Recruit the additional proxy (CP3)250 [sec]Quality degradation430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/SDismiss the core proxies (CP1, CP2)                                                                                                                                                                       | 130 [sec]                                  | Structure transition to CDN         |  |  |

| 250 [sec]Quality degradation430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/SDismiss the core proxies (CP1, CP2)                                                                                                                                                                                                                  |                                            | Recruit the core proxies (CP1, CP2) |  |  |

| 430 [sec]Quality improvement490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/S<br>Dismiss the core proxies (CP1, CP2)                                                                                                                                                                                                                                          | 220 [sec]                                  | Recruit the additional proxy (CP3)  |  |  |

| 490 [sec]Dismiss the additional proxy (CP3)550 [sec]Structure transition to C/SDismiss the core proxies (CP1, CP2)                                                                                                                                                                                                                                                                          | 250 [sec]                                  | Quality degradation                 |  |  |

| 550 [sec]Structure transition to C/SDismiss the core proxies (CP1, CP2)                                                                                                                                                                                                                                                                                                                     | 430 [sec]                                  | Quality improvement                 |  |  |

| Dismiss the core proxies (CP1, CP2)                                                                                                                                                                                                                                                                                                                                                         | 490 [sec]                                  | Dismiss the additional proxy (CP3)  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                             | 550 [sec]                                  | Structure transition to C/S         |  |  |

| 600 [sec] End experiment                                                                                                                                                                                                                                                                                                                                                                    |                                            | Dismiss the core proxies (CP1, CP2) |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                             | 600 [sec]                                  | End experiment                      |  |  |

**т 11 о т**. ...

Table 4: Playback Time-line of Client

| fuble 1. Flayback finde inte of enem |          |         |  |  |

|--------------------------------------|----------|---------|--|--|

| Segment Name                         | Size     | Quality |  |  |

| fileSequence0.ts                     | 926 [KB] | High    |  |  |

| fileSequence1.ts                     | 946 [KB] | High    |  |  |

| fileSequence2.ts                     | 950 [KB] | High    |  |  |

|                                      |          |         |  |  |

| fileSequence26.ts                    | 958 [KB] | High    |  |  |

| fileSequence27.ts                    | 414 [KB] | Low     |  |  |

| fileSequence28.ts                    | 410 [KB] | Low     |  |  |

|                                      |          |         |  |  |

| fileSequence44.ts                    | 414 [KB] | Low     |  |  |

| fileSequence45.ts                    | 958 [KB] | High    |  |  |

| fileSequence46.ts                    | 958 [KB] | High    |  |  |

|                                      |          |         |  |  |

| fileSequence60.ts                    | 967 [KB] | High    |  |  |

| fileSequence61.ts                    | 958 [KB] | High    |  |  |

| fileSequence62.ts                    | 963 [KB] | High    |  |  |

|                                      |          |         |  |  |

to the CDN mode occurred so as to alleviate load concentration. However, the load on the member nodes continued to increase even after the transition, a new member proxy was recruited at the 220th second, and additionally the quality of segments was degraded at the 250th second, and consequently the server withstood the heavy load condition.

On the contrary, in the case of the server without FCAN, we observed that load values were far exceeding ones of the server with FCAN consistently. We, therefore, confirmed that FCAN's features against flash crowds were performed as a result of the increase of client

Figure 7: Comparison of load transitions in On-Demand Experiment

requests, and FCAN archived dynamic load balancing. We obtained equivalent results also in the live streaming experiment.

### 6 Conclusion

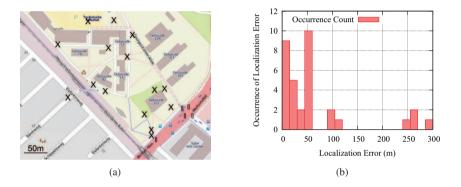

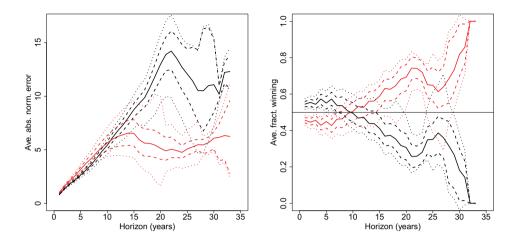

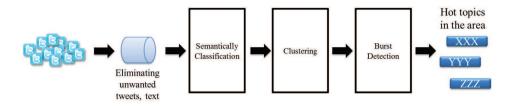

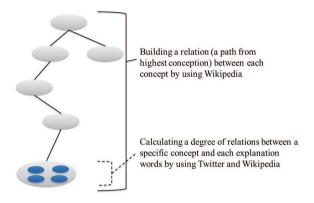

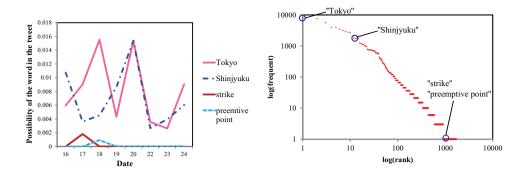

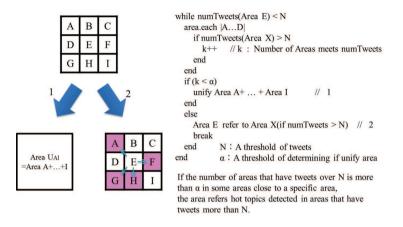

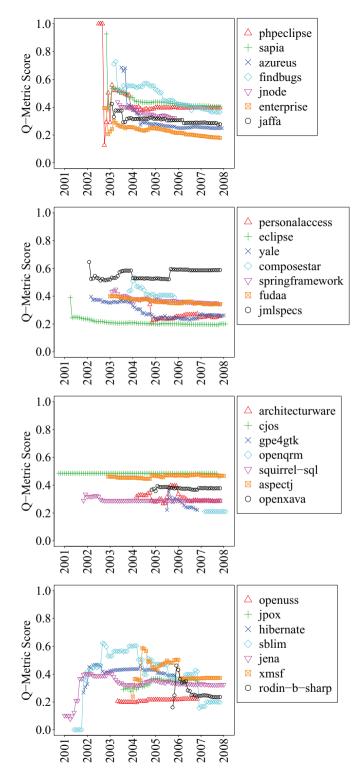

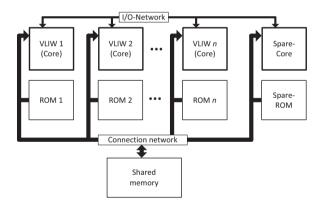

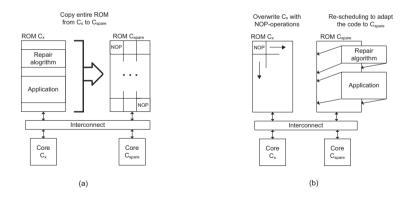

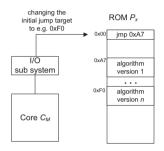

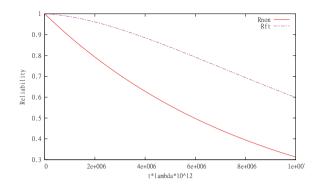

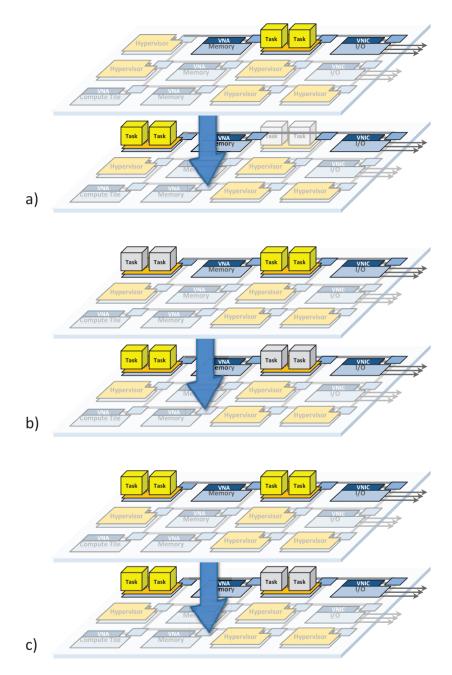

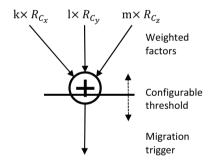

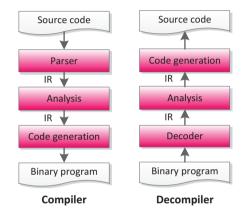

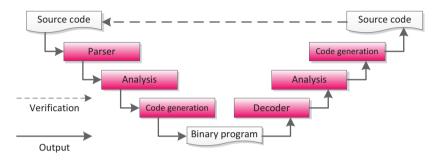

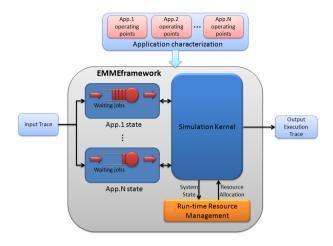

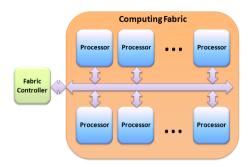

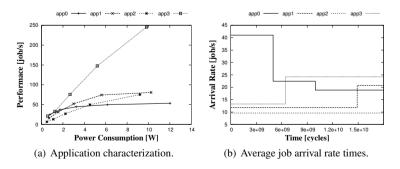

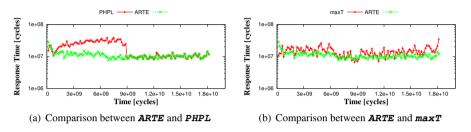

In our preceding studies, FCAN only focused on the static content delivery, however, flash crowds occur also in the video streaming. In order to alleviate flash crowds in the video streaming, both live and on-demand, FCAN adopts a new features such as *dynamic resizing* and *quality restriction* so as to raise a resilience of the system. In this paper, we proposed FCAN's extension for video streaming and demonstrated a prototype of the system on the real Internet. Through some experiments, we confirmed that FCAN's extension works effectively to alleviate flash crowds.